AMD下一代EPYC-E将拥有多达64个“Venice”Zen6核心,引领服务器处理器性能革命

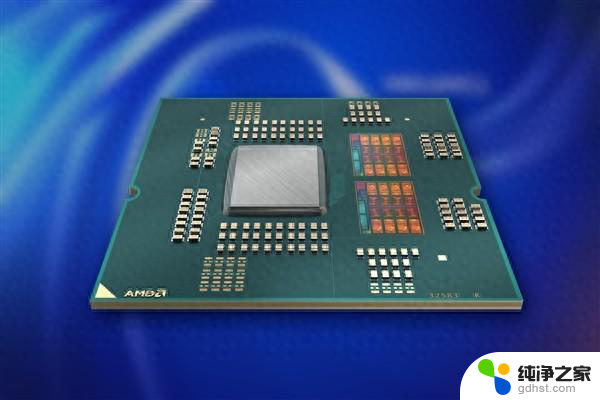

根据摩尔定律已死 (MLD) 的报告,AMD 的下一代 EPYC 系列将采用 Zen6 架构,具有多达 64 个“Venice”Zen6 核心,并支持 PCIe Gen6。AMD的Zen6架构尚未计划在消费市场或数据中心上市。该公司正处于向所有细分市场发布 Zen5 架构的早期阶段,一些 Zen4 产品(Hawk Point、MI300 等)仍在发布中。AMD有一个长期的路线图,先进的计划是在不同市场站稳脚跟的关键。

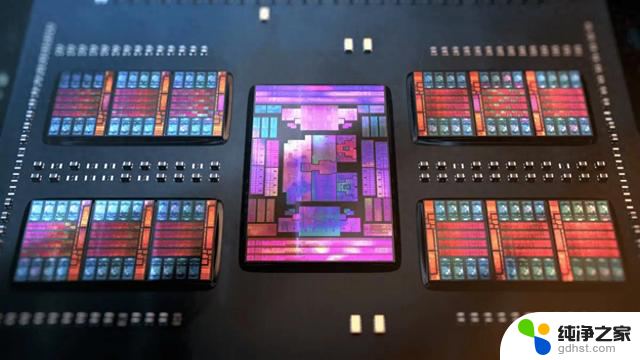

Zen革命即将迎来第六代,采用新的布局设计和新的封装技术,泄密者称这将是Zen5的重大重新设计。AMD 凭借 EPYC(霄龙)系列,将包含 CPU 内核、网络 IP 和定制 FPGA 的小芯片结合在一起。这种方法开辟了各种新的可能性,并逐渐模糊了传统 CPU 和专用加速器之间的区别。

9 月份左右,MLID 直接从 AMD 内部幻灯片分享了 Zen5 和 Zen6 的第一个架构细节。这证实了两种架构的代号都是 Nirvana 和 Morpheus。虽然视频主要关注 Zen5,但有关 Zen6 的更多细节包括 AMD 每个芯片组的核心数量增加(高达 32 个)以及针对 AI 和机器学习的高精度浮点 (FP16) 运算加速。我们确认我们的目标是

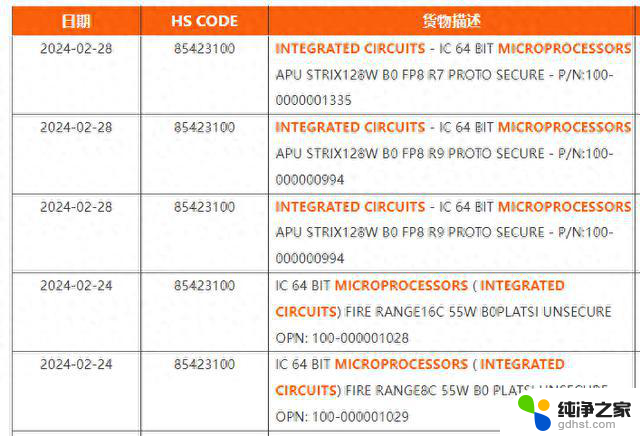

MLID 现已发布其 EPYC-E 产品系列的图表,其中 E 似乎代表 Edge。它专为低核心数和低功耗的通信和边缘系统而设计。所示产品具有 32 个 Zen6 核心,每侧配有 Venice SP8 IOD 和两个 CCD。这种特殊的 CPU 设计还允许将一些 CCD 替换为基于 Pensando Salina 设计的 NCD(网络计算芯片)。

相比之下,用于此 EPYC-E 设计的 SP8 插槽将成为某些 EPYC 系列的下一个 CPU 插槽。预计它将与 SP7 同时推出,后者将搭载更大的 Venice CPU。SP8 是一个小型插座,计划作为 Siena & Sorano 的后继产品。

EPYC-E 将提供两种变体:具有 64 个 Zen6 核心的“标准”版本和具有 32 个核心的“入门”版本。标准版支持八通道 DDR5-6400 内存,支持 64 个 PCIe Gen5 和 32 个 PCIe Gen6 接口。入门级 EPYC-C CPU 具有四通道内存支持以及相同速度的 32 (Gen5) 和 16 (Gen6) PCIe 通道。

一颗 CCD 提供 32 个核心,而入门级 EPYC-E 系列仅限于如此数量的核心,这表明 AMD 可能会用 NCD 瓦片替换其中一个 CCD。同样,在标准版中,两个 Zen6 小芯片可以替换为定制 FGPA 和 NCD。

根据对新文档的访问和一些有根据的猜测,MLID 已经为 SP7 插槽创建了可能的 Zen6 EPYC 处理器的模型。AMD 目前没有对 Zen6 和假设的 Zen6c(云/密集)核心进行区分,但这可能是因为 AMD 正在放弃这种区分,或者没有计划使用这样的核心。无论如何,可能的带有 4 个 IOD 芯片的 8-chiplet 设计是当前的 96 Zen4(热那亚)或 128 Zen4c(贝加莫)设计,以及未来图灵的 128/192 Zen5(经典)或 Zen5(密集)设计,并有可能增加核心数量从核心到256。

AMD下一代EPYC-E将拥有多达64个“Venice”Zen6核心,引领服务器处理器性能革命相关教程

-

-

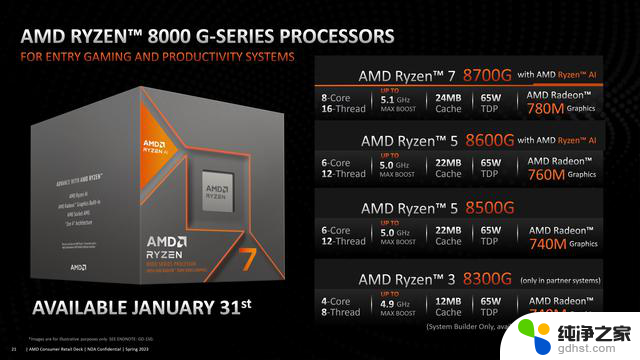

AMD公布Ryzen 8000系列处理器Zen4c内核参数,性能值得关注

AMD公布Ryzen 8000系列处理器Zen4c内核参数,性能值得关注2024-01-23

-

-

AMD Zen5单核性能飙升40%!重现初代Zen的辉煌,性能达到新高度

AMD Zen5单核性能飙升40%!重现初代Zen的辉煌,性能达到新高度2024-03-31

- NVIDIA GeForce GTX 2070 GPU工程样卡曝光 拥有2176个核心,性能如何?

- 微软自研首个64位Arm CPU Cobalt 100商用,领跑ARM处理器市场

- 10核心骁龙X Elite处理器曝光 将搭载于微软Surface 10 Pro,性能强劲,期待上市

- 暑期购电脑,如何选择更安心?英特尔13代、14代处理器崩溃事件引发关注

- AMD 有史以来第一次!重磅发布全新处理器

- 高通骁龙X Plus 8核处理器发布,更便宜的Copilot电脑即将上市

- CPU和GPU有什么区别,玩游戏哪个更重要?如何选择最佳配置?

- 如何激活Windows系统,轻松解决电脑激活问题,快速激活Windows系统步骤指南

- 10-3:WIN7开机进入系统和简介如何操作?详细解析步骤

- 英伟达要去日本造GPU?为何选择日本?

- 国产GPU公司为何扎堆冲刺IPO?要钱、借红利、打知名度

- 英伟达PC端Nvidia应用正式上线,取代GeForce Experience,提升游戏性能和体验

微软资讯推荐

- 1 如何激活Windows系统,轻松解决电脑激活问题,快速激活Windows系统步骤指南

- 2 10-3:WIN7开机进入系统和简介如何操作?详细解析步骤

- 3 英伟达要去日本造GPU?为何选择日本?

- 4 国产GPU公司为何扎堆冲刺IPO?要钱、借红利、打知名度

- 5 英伟达PC端Nvidia应用正式上线,取代GeForce Experience,提升游戏性能和体验

- 6 等等党下山的最好时机,2024年末大促显卡推荐:如何选择性价比最高的显卡?

- 7 详细步骤教你如何在Win7系统中连接网络,快速实现网络连接

- 8 AMD Zen 6处理器Medusa系列发布:桌面、移动端全覆盖

- 9 微软不再喜欢您下载Windows 10 即使是从官方来源,这是为什么?

- 10 微软发布最新Win11 27744 Canary预览版,首次引入Prism技术模拟任意x64应用

win10系统推荐